研究内容

我々の半導体ナノ集積グループは、もはや現代社会で欠かせない電子材料の「半導体」を研究しています。IV族半導体シリコン(Si)等による相補型MOS電界効果トランジスタ(CMOS)や、相補型電界効果トランジスタ(CFET)技術等、2030年代1nmプロセス以降の「次」の材料・デバイスに向けて、従来のSiプラットフォームに適用可能な多彩な異種半導体ナノ材料・デバイス集積技術の研究開発を広く展開し、次世代半導体ナノ材料・物性に係る基礎研究と、半導体ナノエレクトロニクスデバイスの新奇集積技術実現に向けた応用研究の両輪で研究を進めます。「次世代半導体の技術革新はトップダウン微細加工だけで実現できるか?」という技術的な問いに対して、我々半導体ナノ集積グループで目指す基盤材料技術では、「トップダウン、ボトムアップ、いずれか一方の技術だけで全てを実現する必要はない」という自由な発想から、当グループリーダーらがこれまで独自に培ってきた垂直自立型半導体ナノワイヤのようなナノ構造のボトムアップ位置制御成長技術を駆使しつつ、益々成熟するトップダウン微細加工や表面活性化常温接合技術等も最大限活かす「いいとこ取り」半導体ナノ集積技術を目指します。

トップダウン+ボトムアップの「いいとこ取り」半導体ナノ材料集積技術

Siプラットフォームの中工程(middle-of-line: MOL)・配線工程(back-end-of-line: BEOL)に向けた集積技術では、例えば400ºC以下のプロセス温度が要求されます。2030年代1nmプロセス以降の次世代半導体トランジスタのチャネル材料として期待される、例えば、遷移金属ダイカルコゲナイド(TMDC)の2次元ナノシート材料の集積技術に対して、デバイス構造上の直接低温成長技術を確立します。これまで培った独自技術を基に、Siプラットフォームにおけるトップダウン微細加工で実現する次世代半導体CFET等のデバイス構造上で、2次元TMDCナノシート単結晶のチャネル材料を、欲しい場所にだけ直接結晶成長可能な(有機金属気相成長(MOVPE)法、化学気相堆積(CVD)法等による)ボトムアップ位置制御成長技術の確立を目指します。

ボトムアップでしか実現し得ない新奇半導体ナノ材料の集積技術

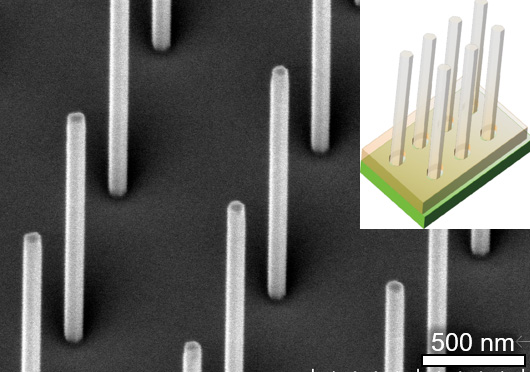

一方、従来型の薄膜結晶成長では実現困難な半導体ヘテロ接合ナノ構造、とりわけ本グループリーダーらによる独自の縦型ナノワイヤ構造化により、バルク・薄膜では存在しない結晶構造や特異な電子物性を実現可能です。例えば、比較的高温での結晶成長や特殊な結晶面方位ウェハが必要なIII-V族あるいはIV族半導体縦型(垂直自立型)ヘテロ接合ナノワイヤ等の場合、前工程(front-end-of-line: FEOL)におけるボトムアップ位置制御成長(MOVPE法、CVD法等)の後、表面活性化常温接合等、Si上の貼り合わせ技術により、ウェハ結晶面方位を問わず、Siプラットフォーム上で異種半導体ナノ材料集積を実現する技術を目指します。図は、半導体薄膜を上から削る(エッチングする)トップダウン微細加工手法ではなく、下(半導体ウェハ: 図の場合SiやGaAs等の異種材料結晶ウェハ)から直接結晶成長するボトムアップ位置制御結晶成長手法により作製した、III-V族半導体である垂直自立型InAsナノワイヤの周期アレイ構造の走査電子顕微鏡像(鳥瞰像)。