# A 6.75F<sup>2</sup>/BIT VOLTAGE-CONTROL SPINTRONICS MEMORY ARRAY BY TWO MEMORY LAYERS STACKING AND BURIED-WORDLINE CELL TRANSISTORS

# Satoshi TAKAYA, Kazutaka IKEGAMI, Shinobu FUJITA, Naoharu SHIMOMURA, and Hiroaki YODA

Corporate R&D Center, Toshiba Corporation, Kawasaki, Japan

satoshi1.takaya@toshiba.co.jp

## I. INTRODUCTION

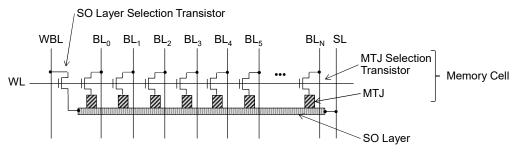

Voltage-Control Spintronics Memory (VoCSM) [1] is proposed as high density and low power nonvolatile memory to replace Dynamic Random Access Memory (DRAM). However, VoCSM cell contains 8 magnetic tunnel junctions (MTJs) and 9 access transistors in 1 string unit which stores 8 bits (Fig. 1). To reduce cell area, we should improve layout of cell unit. In high density 6 F<sup>2</sup>/bit DRAM cell layout, the buried word lines and the slanted angle of active area patterns are mostly used [2]. When we adapt these high density DRAM cell techniques to the cell layout, high density VoCSM can be realized.

### II. VOLTAGE-CONTROL SPINTRONICS MEMORY

The VoCSM string contains 8 MTJs and 9 access transistors. Each source node of the access transistors is connected to bitlines (BLs), and gate node of the access transistors is connected to wordline (WL). The SO layer is the bottom electrode of MTJs and connected to the selection transistor and source line (SL). To realize high density VoCSM, we should layout these elements in the small area.

#### III. HIGH DENSITY CELL LAYOUT

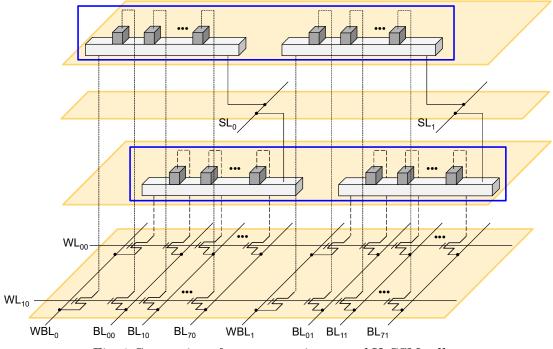

The 6  $F^2$  DRAM layout that contains 1 access transistor and via to storage node. The layout can be realized by using the buried word lines and the slanted angle of active area patterns. When we connect the vias to the storage node to the top electrodes of the MTJ, high density cell layout can be realized. However, there is no space to layout MTJ string and connection vias to top electrode of MTJ in same layer, we share the space to next column and stack 2 memory layers (Fig. 2). The first layer contains the access transistors of 2 strings of the VoCSM cell. The second layer contains the vias to both of the VoCSM strings and one of the VoCSM string. The third layer is the connection space to SL. The fourth layer contains the other VoCSM string. Then the 8-bit VoCSM string can be layouted above 9 access transistors which total area is 54  $F^2$ , and the cell area is 6.75  $F^2$ /bit.

# **IV. CONCLUSIONS**

The 6.75  $F^2$ /bit class VoCSM cell layout is proposed. We adapt the high density memory cell techniques and 2 memory layers stacking to the layout.

#### ACKNOWLEDGEMENTS

The authors would like to thank K. Abe for her technical contributions. This work was funded by ImPACT Program of Council for Science, Technology and Innovation (Cabinet Office, Government of Japan).

> Satoshi Takaya E-mail: satoshi1.takaya@toshiba.co.jp tel: +81-44-549-2212

# DP-17

# REFERENCES

- H. Yoda, N. Shimomura, Y. Ohsawa, S. Shirotori, Y. Kato, T. Inokuchi, Y. Kamiguchi, B. Altansargai, Y. Saito, K. Koi, H. Sugiyama, S. Oikawa, M. Shimizu, M. Ishikawa, K. Ikegami, and A. Kurobe, " Voltage-Control Spintronics Memory (VoCSM) Having Potentials of Ultra-Low Energy-Consumption and High-Density," 2016 IEEE International Electron Devices Meeting (IEDM), pp. 27.6.1-27.6.4, 2016.

- 2) T. Schloesser, F. Jakubowski, J. v. Kluge, A. Graham, S. Slesazeck, M. Popp, P. Baars, K. Muemmler, P. Moll, K. Wilson, A. Buerke, D. Koehler, J. Radecker, E. Erben, U. Zimmermann, T. Vorrath, B. Fischer, G. Aichmayr, R. Agaiby, W. Pamler, T. Schuster, W. Bergner, and W. Mueller, "6F<sup>2</sup> Buried Wordline DRAM Cell for 40nm and Beyond," 2008 IEEE International Electron Devices Meeting (IEDM), pp. 809-812, 2008.

Fig. 1 A schematic drawing of the VoCSM.

Fig. 2 Connection of access transistors and VoCSM cells.